# Curriculum 2021

## **B. Tech. Electronics and Communication Engineering**

(Duration of Study : 4 years)

## Department of Electronics and Communication Engineering GMR Institute of Technology

Rajam, Andhra Pradesh (An Autonomous Institute Affiliated to JNTU-GV, Vizinagram, AP) NBA Accredited and NAAC Accredited

#### The Vision of GMRIT

- To be among the most preferred institutions for engineering and technological education in the country

- An institution that will bring out the best from its students, faculty and staff to learn, to achieve, to compete and to grow – among the very best

- An institution where ethics, excellence and excitement will be the work religion, while research, innovation and impact, the work culture

#### **The Mission of GMRIT**

- To turnout disciplined and competent engineers with sound work and life ethics

- ✤ To implement outcome based education in an IT-enabled environment

✤ To encourage all-round rigor and instill a spirit of enquiry and critical thinking among students, faculty and staff

✤ To develop teaching, research and consulting environment in collaboration with industry and other institutions

#### **Department Vision**

To be a nationally preferred department of learning for students and teachers alike, with dual commitment to research and serving students in an atmosphere of innovation and critical thinking.

#### **Department Mission**

- 1. To provide high-quality education in Engineering to prepare the graduates for a rewarding career in Electronics and Communication Engineering and related industries, in tune with evolving needs of the industry.

- 2. To prepare the students to become thinking professionals and good citizens who would apply their knowledge critically and innovatively to solve professional and social problems.

#### **Program Educational Objectives**

- PEO 1: Embrace technical and professional skills with the spirit of learning, critical thinking while acquiring the fundamentals in science and technology.

- PEO 2: Contemplate real life problems, design and develop novel products that are technically viable, economically feasible and socially acceptable.

- PEO 3: Encompass ethical values, exhibit soft skills in management & teamwork acquiring leadership qualities.

#### **Program Outcomes**

Engineering graduate will be able to

- PO 1: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.(Engineering knowledge)

- PO 2: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.(Problem analysis)

- PO 3: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations. (Design/development of solutions)

- PO 4: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.(Conduct investigations of complex problems)

- PO 5: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.(Modern tool usage)

- PO 6: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.(The engineer and society)

- PO 7: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.(Environment and sustainability)

- PO 8: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.(Ethics)

- PO 9: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.(Individual and team work)

- PO 10: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.(Communication)

- PO 11: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.(Project management and finance)

- PO 12: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.(Life-long learning)

- PSO 1: Apply the knowledge of technological evolutions, model / characterize devices and design the integrated circuits to build analog and digital systems. (Program Specific)

- PSO 2: Understand and apply the fundamentals of communication and signal processing to develop systems wrapped with industry standard protocols and standards. (Program Specific)

# Department of Electronics and Communication Engineering Minimum Credits to be earned: 160 (for Regular Students) 127 (for Lateral Entry Students)

Einst Come oster

| Firs | First Semester |                                  |               |       |   |           |         |

|------|----------------|----------------------------------|---------------|-------|---|-----------|---------|

| No   | Course         | Course                           | POs           |       |   | act Hours |         |

| INU  | Code           | course                           | FUS           | L     | Т | P         | C       |

| 1    | 21HSX01        | Communicative English            | 10, 12        | 2     | - | -         | 2       |

| 2    | 21MAX01        | <b>Engineering Mathematics I</b> | 1             | 3     | - | -         | 3       |

| 3    | 21PYX01        | Engineering Physics /            | 1 / 1         | 2/2   |   |           | 2/2     |

| 3    | 21CYX01        | Engineering Chemistry            | 1/1           | 3/3   | - | -         | 3/3     |

| 4    | 21BEX01        | Basics of Engineering /          | 1 1 2 / 1 1 2 | 27    |   | 12        | 2 /1 ⊏  |

| 4    | 21BEX06        | IT Workshop                      | 1,12/1,12     | 3/-   | - | -/3       | 3/1.5   |

| 5    | 21BEX02        | Problem Solving and              | 1 1 2         | 3     |   |           | 3       |

| Э    | ZIDEAUZ        | Programming Skills               | 1,12          | 3     | - | -         | 3       |

| 6    | 21BEX03        | Problem Solving and              | 4             |       | _ | 3         | 1.5     |

| 0    |                | Programming Skills Lab           |               | -     | - | 3         | 1.5     |

|      | 21BEX04/       | Engineering Drawing /            | 1,5,10/1,9,10 |       |   |           |         |

| 7    | 21BEX05        | e e.                             | 1,5,10/1,9,10 | -     | - | 3/3       | 1.5/1.5 |

|      |                | Engineering Workshop             |               |       |   |           |         |

| 8    | 21PYX02/       | Engineering Physics Lab          | A / A         |       |   | 2/2       | 1 Г     |

| 8    | 21CYX02        | /Engineering Chemistry Lab       | 4/4           | -     | - | 3/3       | 1.5     |

| 9    |                | Communicative English Lab/-      | 10,12         |       |   | 3/-       | 1.5/-   |

| 9    | 21HSX02/-      |                                  | 10,12         | -     | - | 3/-       | 1.5/-   |

|      |                |                                  | Total         | 14/11 | 0 | 12/12     | 20/17   |

| Seco | ond Semeste    | r                                |               |       |   |           |         |

| 1    |                | Language Elective                | 10,12         | 2     | - | -         | 2       |

| 2    | 21MAX02        | Engineering Mathematics II       | 1             | 3     | - | -         | 3       |

|      | 21CYX01/       | Engineering Chemistry            |               |       |   |           |         |

| 3    | 21PYX01        | /Engineering Physics             | 1/1           | 3/3   | _ | -         | 3/3     |

| 0    | 211 1/101      | / Engineering r nystes           | 1/1           | 575   |   |           | 575     |

|      | 21BEX01/       | Basics of Engineering/           |               | 12    |   |           |         |

| 4    | 21BEX06        | IT Workshop                      | 1,12/1,12     | -/3   | - | 3/-       | 1.5/3   |

| 5    | 21BEX07        | Python Programming               | 1,12          | 3     | - | -         | 3       |

| 6    | 21BEX08        | Python Programming Lab           | 4             | -     | - | 3         | 1.5     |

| -    | 21BEX05/       |                                  |               |       |   | -         |         |

| 7    | 21BEX04        | Engineering Workshop /           | 1,9,10/1,5,10 | -     | _ | 3/3       | 1.5/1.5 |

| ,    |                | Engineering Drawing              | 1,7,10,10,10  |       |   | 0,0       | 110/110 |

|      | 21CYX02/       | Engineering Chemistry            |               |       |   |           |         |

| 8    | 21PYX02        | Lab/Engineering Physics Lab      | 4/4           | -     | - | 3/3       | 1.5/1.5 |

|      | -/21HSX02      |                                  |               |       |   |           |         |

| 9    | /211101102     | -/Communicative English Lab      | -/10,12       | _     | _ | -/3       | -/1.5   |

| -    |                | ,                                | , ,           |       |   | , -       | ,       |

|      |                |                                  | Total         | 11/14 | 0 | 12/12     | 17/20   |

| Thi  | rd Semester    |                                  |               | 1     | - | ,         |         |

| 1    | 21MA301        | Complex Variables                | 1, PSO2       | 3     | - | -         | 3       |

| 2    | 21EC301        | Electronic Devices and Circuits  | 1,2,PS01      | 3     | - | -         | 3       |

| 3    | 21EC302        | Linear Circuit Analysis          | 1,2,4,5, PSO1 | 3     | - | 2         | 4       |

| 4    | 21EC303        | Logic Circuit Design             | 1,2, PS01     | 3     | - | -         | 3       |

|      | 21EC304        | Random Variables and             | 1,2, PSO2     |       |   |           |         |

| 5    |                | Stochastic Processes             | , ,           | 3     | - | -         | 3       |

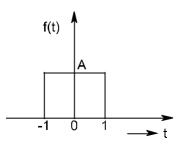

| 6    | 21EC305        | Signals & Systems                | 1,2,4,5, PSO2 | 3     | - | 2         | 4       |

|      |                | Electronic Devices and Circuits  |               |       |   |           |         |

| 7    | 21EC306        | Lab                              | 1, 2, 4, PSO1 | -     | - | 3         | 1.5     |

| 0    |                |                                  | 1, 2, 4, 5,   |       |   |           |         |

| 8    | 21EC307        | Logic Circuit Design Lab         | PSO1          | -     | - | 3         | 1.5     |

| 9    | 21ESX01        | Employability Skills I           | 1,2,5,8,10,12 | -     | - | 2         | -       |

| 10   | 21HSX11        | CC & EC Activities I             | 6,7,9,10      | -     | - | 1         | -       |

|        |                    |                                         | Total                | 18 | 0 | 13       | 23       |

|--------|--------------------|-----------------------------------------|----------------------|----|---|----------|----------|

|        | irth Semeste       |                                         |                      |    |   |          |          |

| 1      | 21CSE01            | Object Oriented Programming             | 1,2,5                | 3  | - | -        | 3        |

| 2      | 21EC401            | Analog and Digital                      | 1,2, PSO2            | 3  | - | -        | 3        |

| 0      | 2150402            | Communications                          | 1.2.45.0004          |    |   | 2        |          |

| 3      | 21EC402            | Analog Electronic Circuits              | 1, 2, 4,5, PSO1      | 3  | - | 2        | 4        |

| 4      | 2150402            | Electromagnetic Fields and              | 1,2, PSO2            | 2  |   |          | 2        |

|        | 21EC403            | Waves                                   | 1.2.001              | 3  | - | -        | 3        |

| 5      | 21EC404            | Linear Control Systems                  | 1, 2, PSO1,<br>PSO2  | 3  | _ |          | 3        |

|        | 2120404            | Object Oriented Programming             | 1302                 | 3  | - | -        | 5        |

| 6      | 21CSE02            | Lab                                     | 1,2,4,5              | -  | _ | 3        | 1.5      |

| _      |                    | Analog and Digital                      | _)_) _) ]            |    |   |          | 1.0      |

| 7      | 21EC405            | Communications Lab                      | 1, 2, 4,5, PSO2      | -  | - | 3        | 1.5      |

| 8      | 21ESX01            | Employability Skills I                  | 1,2,5,8,10,12        | -  | - | 2        | 2        |

| 9      | 21HSX11            | CC & EC Activities I                    | 6,7,9,10             | -  | - | 1        | 1        |

|        |                    |                                         | Total                | 15 | 0 | 11       | 22       |

| Fift   | h Semester         |                                         |                      | -  |   |          |          |

|        | 21EC501            | Linear and Digital IC                   | 1,2, PSO1            | 2  |   |          | 2        |

| 1      |                    | Applications                            | , ,                  | 3  | - | -        | 3        |

| 2      | 21EC502            | Microprocessors and                     | 1, 2, 3, 4, 5,       | 2  |   | n        | 4        |

| 2      |                    | Microcontrollers                        | PSO1                 | 3  | - | 2        | 4        |

| 3      | 21EC503            | VLSI Design                             | 1, 2, 3, 4, 5,       | 3  | - | 2        | 4        |

| 3      |                    |                                         | PSO1                 | 3  | - | 2        | 4        |

| 4      | 21EC504            | Antennas and Microwave                  |                      | 3  | - | _        | 3        |

|        |                    | Engineering                             | 1,2, PSO2            |    |   |          |          |

| 5      |                    | Elective I (Professional Elective )     |                      | 3  | - | -        | 3        |

| 6      |                    | Elective II (Open Elective I)           |                      | 3  | - | -        | 3        |

| 7      | 21EC505            | Linear IC Applications Lab              | 1,2,3, 4, PSO1       | -  | - | 3        | 1.5      |

| 8      | 21TPX01            | Term Paper                              | 1,4,10,12            | -  | - | 3        | 1.5      |

| 9      | 21ESX02            | Employability Skills II                 | 1,2,5,8,10,12        | -  | - | 2        | -        |

| 10     | 21HSX12            | CC & EC Activities II                   | 6,7,9,10             | -  | - | 1        | -        |

| 11     | 21SIX01            | Summer Internship I                     | 1,2,8,10,12          | -  | - | -        | 1        |

|        |                    |                                         | Total                | 18 | 0 | 13       | 24       |

|        | th Semester        |                                         |                      |    |   |          |          |

| 1      | 21HSX10            | Engineering Economics and               | 10,11,12             | 3  | _ | -        | 3        |

| -      |                    | Project Management                      |                      | 5  |   |          | 5        |

| 2      | 21EC601            | Cellular and Mobile                     | 1.0.000              | 3  | - | -        | 3        |

|        | 2450(02            | Communications                          | 1,2, PSO2            |    |   |          |          |

| 3      | 21EC602            | Digital Signal Processing               | 1,2, PSO2            | 3  | - | -        | 3        |

| 4      |                    | Elective III<br>(Professional Elective) |                      | 3  |   | 2        | 4        |

| 5      |                    | Elective IV (Open Elective II)          |                      | 3  | - | <u> </u> | 3        |

| 6      | 21EC603            | Digital Signal Processing Lab           | 1,2,4,5, PSO2        | -  | - | 3        | 1.5      |

| 7      |                    |                                         |                      |    | - | 3        |          |

| / 8    | 21MPX01<br>21ESX02 | Mini Project<br>Employability Skills II | ALL<br>1,2,5,8,10,12 | -  | - | 2        | 1.5<br>2 |

| 8<br>9 | 21ESX02<br>21HSX12 | CC & EC Activities II                   | 6,7,9,10             | -  | - | 1        | 1        |

| 9      | 21H5X12<br>21ATX01 | Environmental Studies                   |                      | -  |   | 1        | 1        |

|        | 21ATX01<br>21ATX02 | Human Values and Professional           | 1,6,7,12             | -  | - | -        |          |

| 11     | LIAIAUL            | Ethics                                  |                      | -  |   | -        | _        |

| 12     | 21ATX              | Audit Course                            |                      | _  | - | -        | _        |

|        |                    |                                         | Total                | 15 | 0 | 11       | 22       |

| Sev    | enth Semest        | ter                                     | i otul               | 10 | v | ••       |          |

| 1      | 21PWX01            | Project Work                            | ALL                  | -  | - | 16       | 8        |

| 2      |                    | Elective V (Professional Elective)      |                      | 3  | - | -        | 3        |

|        |                    | Elective VI                             |                      | 0  |   |          |          |

| 3      |                    | (Professional Elective)                 |                      | 3  | - | -        | 3        |

| 4      |                    | Elective VII (Open Elective III)        |                      | 3  | - | -        | 3        |

| •      |                    |                                         | 1                    | ~  | 1 | 1        |          |

Department of Electronics and Communication Engineering, GMRIT | Curriculum under Academic Regulation 2021

| 5    | 21SIX02         | Summer Internship II                      | 1,2,8,10,12                 | - | - | -  | 1  |

|------|-----------------|-------------------------------------------|-----------------------------|---|---|----|----|

|      |                 |                                           | Total                       | 9 | 0 | 16 | 18 |

| Eigl | Eighth Semester |                                           |                             |   |   |    |    |

| 1    | 21FIX01         | Full Semester Internship (FSI)            | 1,2,5,8,9,10,<br>PSO1, PSO2 | - | - | -  | 8  |

| 2    |                 | Elective VIII (Professional<br>Elective ) |                             | - | - | -  | 3  |

| 3    |                 | Elective IX (Open Elective IV)            |                             | - | - | -  | 3  |

|      |                 |                                           | Total                       | 0 | 0 | -  | 14 |

### List of Electives

| Lang   | Language Electives  |                                                      |                                                                                                   |          |           |           |           |  |

|--------|---------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------|-----------|-----------|-----------|--|

| No.    | Course<br>Code      | Course                                               | POs                                                                                               | Coi<br>L | ntac<br>T | t Ho<br>P | ours<br>C |  |

| 1      | 21HSX03             | Advanced Communicative English                       |                                                                                                   | 2        | -         | -         | 2         |  |

| 2      | 21HSX04             | Communicative German                                 |                                                                                                   | 2        | -         | -         | 2         |  |

| 3      | 21HSX05             | Communicative French                                 |                                                                                                   | 2        | -         | -         | 2         |  |

| 4      | 21HSX06             | Communicative Japanese                               | 10,12                                                                                             | 2        | -         | -         | 2         |  |

| 5      | 21HSX07             | Communicative Spanish                                |                                                                                                   | 2        | -         | -         | 2         |  |

| 6<br>7 | 21HSX08<br>21HSX09  | Communicative Korean<br>Communicative Hindi          |                                                                                                   | 2        | -         | -         | 2         |  |

| -      | tivel               | communicative minui                                  |                                                                                                   | 2        | -         | -         | 2         |  |

|        |                     | , III and Other Core Electives                       |                                                                                                   |          |           |           |           |  |

|        | 21ECC11             | RTL Coding Techniques                                | 1, 2, 3, PSO1                                                                                     | 3        | -         | -         | 3         |  |

| 1      |                     | (Chip Design Career Path)                            |                                                                                                   |          |           |           |           |  |

|        | 21ECC21             | Data Acquisition System                              |                                                                                                   |          |           |           |           |  |

| 2      |                     | (Embedded System Design Career Path)                 | 1, 2, PSO1                                                                                        | 3        | -         | -         | 3         |  |

|        | 21ECC31             | Information Theory and Coding                        | 1, 2, PSO2                                                                                        | 3        | -         | -         | 3         |  |

| 3      | 210001              | Techniques                                           | 1, 2, 1002                                                                                        | 0        |           |           |           |  |

|        |                     | (Communication and Signal Processing)                |                                                                                                   |          |           |           |           |  |

| 4      | 21IT304             | Database Management Systems                          | 1, 2, 3                                                                                           | 3        | _         | -         | 3         |  |

| 5      | 2111304<br>21CS303  | Data Structures                                      | 1, 2, 3                                                                                           | 3        | -         | -         | 3         |  |

| 6      | 21C3303<br>21CS403  |                                                      |                                                                                                   | 3        | -         | -         | 3         |  |

| 0      | 2103403             | Computer Organization and Architecture               | 1,2                                                                                               |          | -         | -         | 3         |  |

| Floc   | tive II:Open        | MOOCs                                                |                                                                                                   | -        | -         | -         | 3         |  |

| 1      | 21CE001             | Disaster Management                                  | 2,7                                                                                               | 3        | -         | -         | 3         |  |

|        |                     | Electrical Installation, Safety and                  |                                                                                                   |          |           |           |           |  |

| 2      | 21EE001             | Auditing                                             | 2,3,6,8                                                                                           | 3        | -         | -         | 3         |  |

| 3      | 21ME001             | Fundamentals of Optimization Techniques              | 1,2,3,5                                                                                           | 3        | -         | -         | 3         |  |

| 4      | 21EC001             | Sensors for Engineering Applications                 | 1                                                                                                 | 3        | -         | -         | 3         |  |

| 5      | 21CS001             | Fundamentals of Artificial Intillegence              | 1,2,3                                                                                             | 3        | -         | -         | 3         |  |

| 6      | 21CH001             | Energy Conversion and Storage Devices                | 1,3,6,7                                                                                           | 3        | -         | -         | 3         |  |

| 7 8    | 21IT001             | Fundamentals of Multimedia                           | 3,5,7                                                                                             | 3        | -         | -         | 3<br>3    |  |

| -      | 21BS001<br>tive III | Nano Materials and Technology                        | 1,12                                                                                              | 3        | -         | -         | 3         |  |

|        |                     | , III and Other Core Electives                       |                                                                                                   |          |           |           |           |  |

| 1      | 21ECC12             | ASIC Verification using system Verilog               | 1, 2, 3,4,5, PSO1                                                                                 | 3        | -         | 2         | 4         |  |

|        |                     | (Chip Design Career Path)                            | , , -, , -,                                                                                       |          |           |           |           |  |

| 2      | 21ECC22             | Embedded System Design and IoT                       | 1, 2, 3, 4, 5, PSO1                                                                               | 3        | -         | 2         | 4         |  |

|        |                     | (Embedded System Design Career Path)                 | _,_,_,_,_,                                                                                        |          |           |           | _         |  |

| 3      | 21ECC32             | Image processing                                     | 1, 2,4,5, PSO2                                                                                    | 3        | -         | 2         | 4         |  |

|        | 2120002             | (Communication and Signal Processing)                | 1, 2, 1,0,1002                                                                                    | 0        |           | -         | -         |  |

| 4      | 21EC004             | Virtual Instrumentation                              | 1, 2, 4, 5, PSO2                                                                                  | 3        | -         | 2         | 4         |  |

| 5      | 21EC005             | Cryptography and Network Security                    | 1, 3, 4, 5, PSO1                                                                                  | 3        | -         | 2         | 4         |  |

| 6      | 21CS503             | Computer Networks                                    | 1,2,4,5,PS01,PS02                                                                                 | 3        | -         | 2         | 4         |  |

|        | tive IV : Ope       |                                                      | ,_, _, <u>,</u> , <u>,</u> <u>,</u> <u>,</u> <u>,</u> <u>,</u> <u>,</u> <u>,</u> <u>,</u> <u></u> |          |           | _         | -         |  |

| 1      | 21CE002             | Air Pollution and Environmental Impact<br>Assessment | 6,7,12                                                                                            | 3        | -         | -         | 3         |  |

| 2      | 21EE002             | Renewable Energy Sources                             | 2,7                                                                                               | 3        | -         | -         | 3         |  |

| 3      | 21ME002             | Principles of Entrepreneurship                       | 1,5,8,11                                                                                          | 3        | -         | -         | 3         |  |

| 4      | 21EC002             | Electronics for Agriculture                          | 1,2                                                                                               | 3        | -         | -         | 3         |  |

|        |                    | f Electronics and Communication Engineering, GMR11   C                    |                          | c neg | ulatio | 11 202 | , <b>1</b> |

|--------|--------------------|---------------------------------------------------------------------------|--------------------------|-------|--------|--------|------------|

| 5      | 21CS002            | Fundamentals of Machine Learning                                          | 2,5                      | 3     | -      | -      | 3          |

| 6      | 21CH002            | Industrial Safety and Hazard<br>Management                                | 1,2,3,6,8                | 3     | -      | -      | 3          |

| 7      | 21IT002            | Fundamentals of Cloud Computing                                           | 2,6,7,8,12               | 3     | -      | -      | 3          |

| 8      | 21BS002            | Advanced Numerical Technquies                                             | 1,2                      | 3     | -      | -      | 3          |

| 9      | 21BS003            | Functional Materials and Applications                                     | 1,4                      | 3     | -      | -      | 3          |

| Elec   | tive V             |                                                                           |                          |       |        |        |            |

| Care   | er Path I, II,     | , III and Other Core Electives                                            |                          |       |        |        |            |

| 1      | 21ECC13            | Analog and mixed signal VLSI design<br>(Chip Design Career Path)          | 1, 2, 3, PSO1            | 3     | -      | -      | 3          |

| 2      | 21ECC23            | Real Time Operating Systems<br>(Embedded System Design Career Path)       | 1,2, PSO1                | 3     | -      | -      | 3          |

| 3      | 21ECC33            | Multimedia communications<br>(Communication and Signal Processing)        | 1, 2, PSO2               | 3     | -      | -      | 3          |

| 4      | 21EC007            | Wireless Sensor Networks                                                  | 1, 2, PSO1, PSO2         | 3     | -      | -      | 3          |

| 5      | 21IT403            | Operating Systems                                                         | 1, 12                    | 3     | -      | -      | 3          |

| 6      | 21CS603            | Software Engineering                                                      | 4, 5, 8, 11, PSO1        | 3     | -      | -      | 3          |

|        | 2100000            | MOOCs                                                                     | 1, 0, 0, 11, 1001        | -     | -      | -      | 3          |

| Elec   | tive VI            |                                                                           |                          | _     |        |        | 5          |

| 1      | 21EC008            | Design for testability                                                    | 1, 2, 3, PSO1            | 3     | -      | -      | 3          |

| 2      | 21EC009            | Biomedical Signal Processing                                              | 1, 2, PSO2               | 3     | -      | -      | 3          |

| 3      | 21EC009            | UHF and EHF communication systems                                         | 1, 2, PSO2               | 3     | _      | -      | 3          |

| 4      | 21EC010<br>21EC010 | Neural Networks and Deep Learning                                         | 1, 2, PSO1, PSO2         | 3     | _      | -      | 3          |

|        | 210010             | MOOCs                                                                     | 1, 2, 1 30 1, 1 302      | -     | -      | -      | 3          |

| Flee   | tive VII:One       | en Elective III                                                           |                          | -     | -      | -      | 5          |

| 1      | 21CE003            | Solid Waste Management                                                    | 2,3,12                   | 3     | -      | -      | 3          |

| 2      | 21EE003            | Fundamentals of Electrical Vehicle<br>Technology                          | 2,3,12                   | 3     | -      | -      | 3          |

| 3      | 21ME003            | Industrial Engineering and Management                                     | 1,10,11,12               | 3     | -      | -      | 3          |

| 4      | 21EC003            | Interfacing and Programming with Arduino                                  | 1,2                      | 3     | -      | -      | 3          |

| 5      | 21CS003            | Data Science for Engineering Applications                                 | 2,3,4                    | 3     | -      | -      | 3          |

| 6      | 21CH003            | Industrial Ecology for Sustainable<br>Development                         | 2,6,7                    | 3     | -      | -      | 3          |

| 7      | 21IT003            | Fundamentals of Mobile Computing                                          | 1,2,7,12                 | 3     | -      | -      | 3          |

| 8      | 21BS004            | Advanced Materials of Renewable Energy                                    | 1,7                      | 3     | -      | -      | 3          |

| 9      | 21BS005            | Applied Linear Algebra for Engineers                                      | 1,12                     | 3     | -      | -      | 3          |

|        |                    | ofessional Elective )                                                     | 1 2 DCO1                 |       |        |        | 3          |

| 1      | 21EC012<br>21EC013 | Real-Time Systems Design and Analysis<br>Image Processing for Engineering | 1, 2, PSO1<br>1, 2, PSO2 | -     | -      | -      |            |

| 2      |                    | Applications                                                              |                          | -     | -      | -      | 3          |

| 3      | 21EC014            | Computer Architecture                                                     | 1, 2, PSO1               | -     | -      | -      | 3          |

|        |                    | n Elective IV                                                             | 22157                    |       |        |        | 2          |

| 1 2    | 21CE019<br>21EE017 | Green Buildings<br>Sustainable Energy                                     | 2,3,4,5,7<br>1,2,12      | -     | -      | -      | 3          |

| 2      | 21EE017<br>21ME018 | Total Quality Management                                                  | 1,2,12                   | -     | -      | -      | 3          |

| 3<br>4 | 21ME018<br>21EC011 | Communication Technologies                                                | 1,10,11,12               | -     | -      | -      | 3          |

| 5      | 21CS020            | Applications of Artificial Intelligence                                   | 2,3,6,7                  | -     | -      | -      | 3          |

| 6      | 2100020<br>21CH016 | Green Technologies                                                        | 1,6,7                    | -     | -      | -      | 3          |

| 7      | 21IT015            | Human Computer Interaction                                                | 1,7                      | -     | -      | -      | 3          |

| 8      | 21BS006            | Handling of Industrial waste and waste water                              | 1,7                      | -     | -      | -      | 3          |

|        |                    |                                                                           |                          |       |        |        |            |

| And              | it Course                      |                                                     |                  |   | - |   |   |

|------------------|--------------------------------|-----------------------------------------------------|------------------|---|---|---|---|

| <b>Auu</b><br>1  | 21AT001                        | Communication Etiquette in Workplaces               | -                | - | - | - | - |

| 2                | 21AT002                        | Contemporary India: Economy, Policy<br>and Society  | -                | - | - | - | - |

| 3                | 21AT003                        | Design The Thinking                                 |                  | - | - | - | - |

| 4                | 21AT003                        | Ethics and Integrity                                | -                | - | - | _ | _ |

| 5                | 21AT005                        | Indian Heritage and Culture                         | -                | - | - | - | - |

| 6                | 21AT006                        | Intellectual Property Rights and Patents            | _                | - | - | - | - |

| 7                | 21AT007                        | Introduction to Journalism                          | -                | - | - | - | - |

| 8                | 21AT008                        | Mass Media Communication                            | -                | - | - | - | - |

| 9                | 21AT009                        | Science, Technology and Development                 | -                | - | - | - | - |

| 10               | 21AT010                        | Social Responsibility                               | -                | - | - | - | - |

| 11               | 21AT011                        | The Art of Photography and Film Making              | -                | - | - | - | - |

| 12               | 21AT012                        | Gender Equality for Sustanibity                     | -                | - | - | - | - |

| 13               | 21AT013                        | Women in Leadership                                 | -                | - | - | - | - |

| 14               | 21AT014                        | Introduction to Research Methodology                | -                | - | - | - | - |

| 15               | 21AT015                        | Climate Change and Circular Economy                 | -                | - | - | - | - |

| DT               | och (Honor                     | e)                                                  |                  |   |   |   |   |

|                  | ech. (Honors<br>pain I VI SI C | s)<br>ircuit Design and Verification                |                  |   |   |   |   |

| 01               | 21ECH11                        | SoC Design                                          | 1,2,PSO1         | 4 | - | - | 4 |

| 02               | 21ECH12                        | CMOS Logic Circuit Design                           | 1, 2, 3, PSO1    | 4 | - |   | 4 |

| 03               | 21ECH12                        | <u> </u>                                            |                  | 4 |   | - | 4 |

| 03               | 21ECH13                        | Low Power VLSI Design                               | 1, 2, 3, PSO1    |   | - | - |   |

|                  |                                | VLSI Fabrication Technology                         | 1,2,3, PSO1      | 4 | - | - | 4 |

| <b>Don</b><br>01 | 21ECH21                        | tics and Automation                                 | 4.2.2.0004       | 4 |   |   | 4 |

|                  |                                | Advanced Controllers                                | 1, 2, 3, PSO1    | 4 | - | - | 4 |

| 02               | 21ECH22                        | Robots and Control                                  | 1, 2, 3, PSO1    | 4 | - | - | 4 |

| 03               | 21ECH23                        | Industrial Automation                               | 1, 2, PSO1, PSO2 | 4 | - | - | 4 |

| 04               | 21ECH24                        | Distributed Embedded systems                        | 1, 2, 3, PSO1    | 4 | - | - | 4 |

|                  |                                | iitive Radio Networks                               |                  |   |   |   |   |

| 01               | 21ECH31                        | Optical Communications                              | 1, 2, PSO2       | 4 | - | - | 4 |

| 02               | 21ECH32                        | MIMO Wireless Communications                        | 1,2,3, PSO2      | 4 | - | - | 4 |

| 03               | 21ECH33                        | Software Defined Radio                              | 1, 2, PSO2       | 4 | - | - | 4 |

| 04               | 21ECH34                        | Wireless and Mobile Networks                        | 1, 2, PSO1       | 4 | - | - | 4 |

|                  |                                | imedia Signal Processing                            | 1                |   |   |   | 1 |

| 01               | 21ECH41                        | Optimization Techniques                             | 1, 2, PSO1, PSO2 | 4 | - | - | 4 |

| 02               | 21ECH42                        | Audio Signal Processing                             | 1,2,3,PSO2       | 4 | - | - | 4 |

| 03               | 21ECH43                        | Statistical Signal Processing                       | 1,2,3,PSO2       | 4 | - | - | 4 |

| 04               | 21ECH44                        | Computer Vision                                     | 1,2,PSO2         | 4 | - | - | 4 |

|                  | ech. (Minors                   |                                                     |                  |   |   |   |   |

| Ene              | rgy Science                    | & Technology                                        | 1                |   |   |   |   |

| 01               | 21CHM11                        | Foundation of Energy Science and Technology         | 1,2,3,5,7,12     | 4 | - | - | 4 |

| 02               | 21CHM12                        | Energy Generation from Waste                        | 1,2,3,4,5        | 4 | - | - | 4 |

| 03               | 21CHM13                        | Energy Storage Systems                              | 1,2,3,6,7        | 4 | - | - | 4 |

| 04               | 21CHM14                        | Hydrogen Energy and Fuel Cells                      | 1,2,3,7          | 4 | - | - | 4 |

|                  | o Science &                    | Technology                                          |                  | 4 |   |   | 1 |

| 01               | 21CHM21                        | Introduction and Characterization of Nano Materials | 1,2,3,7          | 4 | - | - | 4 |

| 02               | 21CHM22                        | Carbon Nanostructures and Applications              | 1,3,4,5          | 4 | - | - | 4 |

| 03               | 21CHM23                        | Energy, Environment & Biomedical<br>Nanotechnology  | 1,2,3,7          | 4 | - | - | 4 |

| 04               | 21CHM24                        | Industrial Applications of Nano<br>Technology       | 2,3,5,7          | 4 | - | - | 4 |

| Env              | ironmental                     | Engineering                                         | 1                | 1 |   |   | 1 |

|                  |                                |                                                     |                  |   |   |   |   |

| 01   | 21CEM11            | Watershed Management                                  | 6,7      | 4 | - | - | 4 |

|------|--------------------|-------------------------------------------------------|----------|---|---|---|---|

| 02   | 210EM11<br>21CEM12 | Industrial Pollution Control and                      |          | 4 |   |   |   |

| 02   | LIGHNIL            | Engineering                                           | 3,6,7,12 | • | - | - | 4 |

| 03   | 21CEM13            | Solid and Hazardous Waste Management                  | 1,3,6,7  | 4 | - | - | 4 |

| 04   | 21CEM14            | Ecology and Environmental Assessment                  | 1,3,6,7  | 4 | - | - | 4 |

|      |                    | gence & Machine Learning                              | 1,0,0,7  | - |   |   | - |

| 01   | 21CSM11            | Fundamentals of AI & Machine Learning                 | 1,12     | 4 | - | - | 4 |

| 02   |                    | Feature Engineering for Machine                       |          | 4 |   |   |   |

| 02   | 21CSM12            | Learning                                              | 1,2,3    | 1 | - | - | 4 |

| 03   | 21CSM13            | Exploratory Data Analytics                            | 1,4      | 4 | - | - | 4 |

| 04   | 21CSM14            | Deep Learning                                         | 1,2,4    | 4 | - | - | 4 |

|      | er Security        | 2000 2000                                             | _)_) 1   | - |   |   | - |

| 01   | 21CSM21            | Fundamentals of Security                              | 1,2      | 4 | - | - | 4 |

| 02   | 21CSM22            | Management of Information Security                    | 3,6,7    | 4 | - | - | 4 |

| 03   | 21CSM23            | Cyber Security                                        | 1,3,4    | 4 | - | - | 4 |

| 04   | 21CSM23            | Cloud Security                                        | 2,3      | 4 | _ | _ | 4 |

|      | a Science & A      |                                                       | 2,0      | 1 |   |   | 1 |

| 01   | 21CSM31            | Data Cleaning                                         | 2,3,4    | 4 | _ | _ | 4 |

| 01   | 21CSM31<br>21CSM32 | Data Engineering                                      | 1,2,3,4  | 4 | - | - | 4 |

| 02   | 21CSM32<br>21CSM33 | Text Analytics                                        | 1,2,4    | 4 | _ |   | 4 |

| 03   | 21CSM33<br>21CSM34 | Social Network and Semantic Analysis                  |          | 4 | - |   | 4 |

|      |                    | ms Programming                                        | 2,4      | 4 | - | - | 4 |

| 01   | 21CSM41            | Programming Fundamentals                              | 1,2,3    | 4 |   | - | 4 |

|      |                    |                                                       |          |   | - |   |   |

| 02   | 21CSM42            | Data Structures & Algorithms                          | 1,2,3,4  | 4 | - | - | 4 |

| 03   | 21CSM43            | Fundamentals of Databases                             | 1,4      | 4 | - | - | 4 |

| 04   | 21CSM44            | Fundamentals of Computer Networks & Operating Systems | 1,2,3    | 4 | - | - | 4 |

| Digi | tal IC Desig       | n                                                     |          |   |   |   |   |

| 01   | 21ECM11            | Fundamentals of VLSI Design                           | 1,2,3    | 4 | - | - | 4 |

| 02   | 21ECM12            | Digital Design using HDL                              | 1,2,3    | 4 | - | - | 4 |

| 03   | 21ECM13            | FPGA Technology                                       | 1,2      | 4 | - | - | 4 |

| 04   | 21ECM14            | Analog and Mixed Signal Design                        | 1,2      | 4 | - | - | 4 |

| Indu | istrial Autor      | mation                                                |          |   |   |   |   |

| 01   | 21ECM21            | Microcontrollers and Interfacing                      | 1,2,3    | 4 | - | - | 4 |

| 02   | 21ECM22            | Sensors and Data Acquisition System                   | 1,2      | 4 | - | - | 4 |

| 03   | 21ECM23            | Fundamentals of Labview                               | 1,2      | 4 | - | - | 4 |

| 04   | 21ECM24            | Medical Robotics                                      | 1,2,3    | 4 | - | - | 4 |

| Com  | munication         | s and Networking                                      | '        |   |   |   |   |

| 01   | 21ECM31            | Principles of Communications                          | 1,2      | 4 | - | - | 4 |

| 02   | 21ECM32            | Coding Theory and Practice                            | 1,2      | 4 | - | - | 4 |

| 03   | 21ECM33            | Ad-hoc and Wireless Sensor Networks                   | 1,2,3    | 4 | - | - | 4 |

| 04   | 21ECM34            | Fundamentals of Multimedia Networking                 | 1,2,3    | 4 | - | - | 4 |

| Avio | onics              |                                                       |          |   |   |   |   |

| 01   | 21ECM41            | Principles of Aerodynamics                            | 1,2      | 4 | - | - | 4 |

| 02   | 21ECM42            | Aircraft Electrical Systems                           | 1,2      | 4 | - | - | 4 |

| 03   | 21ECM43            | Aircraft Instrument Systems                           | 1,2      | 4 | - | - | 4 |

|      | 21ECM45            | Aircraft Communication and Navigational               |          | 4 |   |   |   |

| 04   |                    | Systems                                               | 1,2      |   | - | - | 4 |

|      |                    | rmation System                                        | 1        |   |   |   |   |

| 01   | 21ECM51            | Sensors and Sensing Technology                        | 1,2      | 4 | - | - | 4 |

| 02   | 21ECM52            | Geographic Information Systems                        | 1,2      | 4 | - | - | 4 |

| 03   | 21ECM53            | Digital Image Processing                              | 1,2      | 4 | - | - | 4 |

| 04   | 21ECM54            | Lidar Systems                                         | 1,2      | 4 | - | - | 4 |

| Elec | tric Vehicles      | s and Technology                                      |          |   |   |   |   |

| 01   | 21EEM11            | Introduction to Electric Vehicles<br>Technologies     | 1,2,3    | 4 | - | - | 4 |

| 02   | 21EEM12            | Electrical Drives and Controllers for                 | 1,2,3    | 4 | _ | _ | 4 |

| 02   |                    | Liecultai Drives allu Colluollers Iof                 | 1,2,3    | 4 | - | - |   |

|      |               | Electric Vehicles                                          |                |   |   |   |   |

|------|---------------|------------------------------------------------------------|----------------|---|---|---|---|

| 03   | 21EEM13       | Charging Technology in Electric Vehicles                   | 1,2,3          | 4 | - | - | 4 |

| 04   | 21EEM14       | Computer Vision in Electric Vehicles                       | 1,2,3          | 4 | - | - | 4 |

| Sma  | rt City Mana  | agement                                                    | 1              |   |   |   |   |

| 01   | 21EEM21       | Fundamentals of Smart City                                 | 2,3            | 4 | - | - | 4 |

| 02   | 21EEM22       | Smart City Infrastructure                                  | 1,2,3,5,6,7,11 | 4 | - | - | 4 |

| 03   | 21EEM23       | Computational Methods for Smart City<br>Management         | 3,5            | 4 | - | - | 4 |

| 04   | 21EEM24       | Communication Technologies and<br>Mobility for Smart City  | 2,3            | 4 | - | - | 4 |

| Indu | ıstrial Appli | cations and Control                                        | 1              |   |   |   |   |

| 01   | 21EEM31       | Modeling and Simulations of Industrial Applications        | 1,2,3          | 4 | - | - | 4 |

| 02   | 21EEM32       | Industrial Sensors and Actuators                           | 1,2,3          | 4 | - | - | 4 |

| 03   | 21EEM33       | Programmable Logic Controllers                             | 1,2,3          | 4 | - | - | 4 |

| 04   | 21EEM34       | Control Design for Industrial Applications                 | 1,2,3          | 4 | - | - | 4 |

| Clou | id Applicatio | on Development                                             | '              |   |   |   |   |

| 01   | 21ITM11       | Introduction to Cloud Computing                            | 6,7,12         | 4 | - | - | 4 |

| 02   | 21ITM12       | Introduction to Web Development with HTML, CSS, JavaScript | 1,2,3,9,12     | 4 | - | - | 4 |

| 03   | 21ITM13       | Developing Cloud Native Applications                       | 5,8,10         | 4 | - | - | 4 |

| 04   | 21ITM14       | Developing Cloud Apps with Node.js and<br>React            | 5,8,10         | 4 | - | - | 4 |

| Rob  | otics and Au  | Itomation                                                  | '              |   |   |   |   |

| 01   | 21MEM11       | Introduction to Robotics                                   | 1,2,3          | 4 | - | - | 4 |

| 02   | 21MEM12       | Drives and Sensors                                         | 1,2,3,4        | 4 | - | - | 4 |

| 03   | 21MEM13       | Control Systems for Robotics                               | 1,2,3,4        | 4 | - | - | 4 |

| 04   | 21MEM14       | Machine Learning for Robotics                              | 2,5            | 4 | - | - | 4 |

| Indu | istrial Syste | ms Engineering                                             |                |   |   |   |   |

| 01   | 21MEM21       | Industrial Management                                      | 1,10,11,12     | 4 | - | - | 4 |

| 02   | 21MEM22       | Fundamentals of Operations Research                        | 1,2,3,5        | 4 | - | - | 4 |

| 03   | 21MEM23       | Enterprise Resource Planning                               | 1,2,3,5,11,12  | 4 | - | - | 4 |

| 04   | 21MEM24       | Production Planning and Control                            | 1,2,3,5,11,12  | 4 | - | - | 4 |

#### 21MA301 Complex Variables

(Programme: ECE)

#### **Course Outcomes**

- 1. Understand the knowledge of Bessel's and Legendre's functions for solving engineering problems

- 2. Infer the calculus of complex valued functions with Cauchy-Riemann equations

- 3. Use Cauchy's theorem and Integral formulae to compute complex integrals

- 4. Outline the singularities of complex variable function Taylor's, Laurent's series

- 5. Select Residue theorem to determine various types of definite integrals

- 6. Compute calculus of complex functions and conformal mappings

#### **COs – POs Mapping**

| COs | P01 | PSO <sub>2</sub> |  |  |  |  |  |

|-----|-----|------------------|--|--|--|--|--|

| 1   | 2   | 2                |  |  |  |  |  |

| 2   | 2   | 2                |  |  |  |  |  |

| 3   | 3   | 3                |  |  |  |  |  |

| 4   | 3   | 3                |  |  |  |  |  |

| 5   | 3   | 3                |  |  |  |  |  |

| 6   | 3   | 3                |  |  |  |  |  |

3-Strongly linked | 2-Moderately linked | 1-Weakly linked

#### Unit I Special Functions

Bessel functions – Generating function, Jacobi series, Recurrence relations, Orthogonality, related problems Legendre's functions- Generating function, Rodrigue's formula, Recurrence relations, Orthogonality, related problems

Chebyshev's polynomials of first kind and second kind

#### Unit II

#### Functions of a complex variable and complex integration

Functions of a complex variable – Continuity, Differentiability, Analyticity, Properties, Cauchy-Riemann equations in Cartesian and polar coordinates (without proof), Harmonic and conjugate harmonic functions, Milne – Thomson method

Complex integration- Line integral, evaluation along a path and by indefinite integration, Cauchy's integral theorem, Cauchy's integral formula, Generalized integral formula (without proofs)

Elementary functions: General and principal values of elementary functions

#### Unit III

#### Complex power series and contour integration

Complex power series- Radius of convergence, Taylor's series, Maclaurin's series and Laurent series (without proofs)

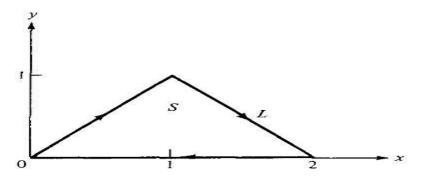

Singular point –Types of singularities, Residue – Evaluation of residues, Residue theorem (without proof) Evaluation of integrals of the type

(a) Improper real integrals

$$\int_{-\infty}^{\infty} f(x) dx$$

(b)  $\int_{c}^{c+2\pi} f(\cos\theta, \sin\theta) d\theta$  (c)  $\int_{-\infty}^{\infty} e^{imx} f(x) dx$

The Laplace inversion integral-Stability Criteria and evaluation of integrals by indentation

12 Hours

#### 3003

12 Hours

**12 Hours**

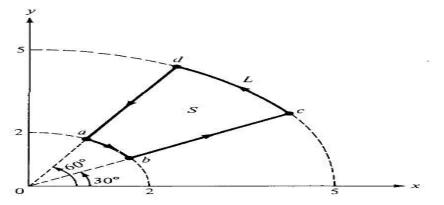

#### Unit IV Calculus of complex functions and conformal mappings

Argument principle, Rouche's theorem - determination of number of zeros of complex polynomials, Maximum Modulus principle, Fundamental theorem of Algebra, Liouville's Theorem (Theorems without proof)

Conformal mapping -Translation, rotation, inversion, Transformation by  $e^{z}$ ,  $z^{2}$ ,  $z^{n}$  (n positive integer), sin z,  $\cos z, z + a/z$

Bilinear transformation – fixed point, properties, invariance of circles and cross ratio, determination of bilinear transformation

The Schwartz-Christoffel Transformation

#### Textbook (s)

**12Hours Total: 48 Hours**

- 1. R.K.Jain and S. R. K Iyengar, Advanced Engineering Mathematics, Narosa Publishing House, 4<sup>th</sup> Edition, New Delhi, 2014 B.S.Grewal, Higher Engineering Mathematics, Khanna Publishers,42<sup>nd</sup> Edition, New Delhi, 2012 B. V. Ramana , Engineering Mathematics, Tata McGraw Hill, New Delhi, 4<sup>th</sup> Edition,2009

- 2. 3.

#### Reference (s)

- 1. Kreyszig, Irvin, Advanced Engineering Mathematics, Wiley India Pvt. Ltd, 9th Edition, 2012

- T.K.V. Iyengar et. al, Engineering Mathematics, Volume-III, S. Chand Co., 2<sup>nd</sup>Edition, New Delhi, 2007 2.

- Ray Wylie and C.Louis Barrett, Advanced Engineering Mathematics, Tata McGraw-Hill PublishingCom. Ltd, 6th Edition, 2003

#### **SAMPLE QUESTION (S)**

#### **Internal Assessment Pattern**

| Cognitive Level | Int. Test 1 (%) | Int. Test 2 (%) | Open book exam<br>(%) |

|-----------------|-----------------|-----------------|-----------------------|

| Remember        | 10              | 10              | -                     |

| Understand      | 30              | 30              | -                     |

| Apply           | 60              | 60              | 70                    |

| Analyze         | -               | -               | 30                    |

| Evaluate        | -               | -               | -                     |

| Create          | -               | _               | -                     |

| Total (%)       | 100             | 100             | 100                   |

#### Remember

- 1. State the steps involved in solving difference equation using Z-transforms.

- 2. Define analytic function and write C-R equations in polar form.

#### Understand

1. Prove that

$$\int_{C} \frac{dz}{z-a} = 2\pi i$$

where C is  $|z-a| = r$

2. Interpret the transformation  $w = \frac{1}{z}$  to find the image of |z - 2i| = 2 in complex plane.

#### Apply

- Use Z-transforms to solve difference equation u<sub>n+2</sub> u<sub>n</sub> = 2<sup>n</sup> with u<sub>0</sub> = 0 and u<sub>1</sub> = 1.

Implement residue theorem to evaluate the definite integral ∫ f(z)dz over the circle |z| = 2.5

and

$$f(z) = \frac{z^2}{(z-1)^2(z+2)}$$

.

#### Analyze

- 1. Classify singularities of a complex valued function and also illustrate the examples for different types of singularities.

- 2. Justify that the function  $f(z) = \sqrt{|xy|}$  is not analytic at the origin, although C-R equations are satisfied at that point.

- 3. Let  $\phi(x, y)$  be an electrical potential in the region that satisfies the boundary values

$$\phi(x, y) = \begin{cases} 100 \quad for \quad C_1 = \left\{ z = e^{i\theta} : 0 < \theta < \frac{\pi}{2} \right\} \\ 0 \quad for \quad C_2 = \left\{ z = e^{i\theta} : \frac{\pi}{2} < \theta < 2\pi \right\} \\ \dots \dots (1)$$

and  $w = f(z) = \frac{(1-i)(z-i)}{(z-1)}$  is a conformal mapping which maps the unit disc onto the upper half plane.

Here z = x + iy is a point in xy - plane and w = u + iv is a point in uv - plane. [**Open Book Examination Question**]

- a) Compute the transformed boundary conditions.

- b) Determine the electrical potential in the unit disc satisfying the boundary conditions.

- c) Estimate the electrical potential in the region bounded by triangle whose vertices are (0,0), (1,0) and (0,1) satisfying the given boundary conditions using suitable conformal mapping.

- 4. If F(z) = -ikz(k > 0) describes a uniform flow upward, which can be interpreted as a uniform flow between two parallel lines,

- a. What happens to the flow if you replace z by  $ze^{-i\pi}$  in  $F^{?}(z)$ b. Obtain a flow around a corner using suitable conformal mapping.

[Open Book Examination Question]

#### 21EC301 Electronic Devices and Circuits

#### **Course Outcomes**

- 1. Explain operation of semiconductor devices, characteristics and their applications

- 2. Illustrate the characteristics of BJT and JFET

- 3. Construct different biasing circuits for BJT

- 4. Illustrate h-parameter representation and Hybrid-model of transistor

- 5. Analyse low frequency and high frequency single stage amplifiers

- 6. Construct multi stage amplifiers

#### **COs – POs Mapping**

| COs | P0 <sub>1</sub> | PO <sub>2</sub> | PSO <sub>1</sub> |

|-----|-----------------|-----------------|------------------|

| 1   | 2               |                 | 2                |

| 2   | 2               |                 | 2                |

| 3   | 3               | 2               | 3                |

| 4   | 2               |                 | 2                |

| 5   | 3               | 2               | 3                |

| 6   | 3               | 2               | 3                |

3-Strongly linked | 2-Moderately linked | 1-Weakly linked

#### Unit I

#### Semiconductors-Diodes

PN junction diode - Forward bias and Reverse bias, Volt-ampere characteristics of p-n diode, Transition and Diffusion capacitances, Zener diode characteristics, Tunnel Diode characteristics - Energy band diagrams, UJT characteristics and SCR characteristics. Rectifiers - Half wave rectifier, Full wave center Tapped , Bridge rectifier, Capacitor filter, Regulator using Zener diode.

Special diodes and it's applications

#### Unit II

#### **BJT & FET**

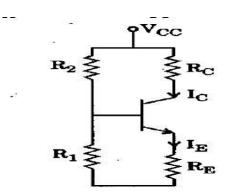

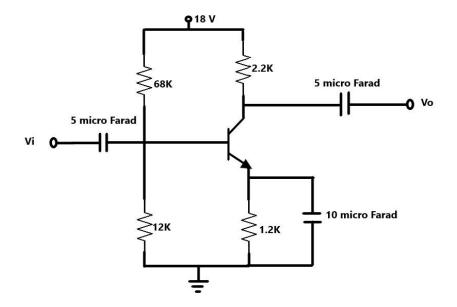

Bipolar Junction transistors - Transistor current components, Transistor as an amplifier, Relation between Alpha and Beta, Input and Output characteristics of Common Base and Common Emitter configurations, BJT biasing - Criteria for fixing operating point, Fixed bias, Collector to base bias, Self-bias, Stabilization techniques, Compensation techniques- Compensation against variation in VBE and Ico, Thermal run away, Thermal stability, Characteristics of JFET.

MOSFET characteristics- Enhancement mode and depletion mode

#### Unit III

#### **Low Frequency Amplifiers**

h-parameter representation of a transistor, Analysis of single stage transistor amplifier using h-parameters -Voltage gain, Current gain, Input impedance and Output impedance of CE, CB, and CC amplifiers using exact and approximate analysis. Miller's and Dual of Miller's theorem.

Analysis of single stage FET amplifiers - voltage gain, input impedance and output impedance of CS, CG, and CD amplifiers.

Buffer amplifier, MOSFET Amplifier

#### Unit IV

#### **High Frequency and Multi Stage Amplifiers**

Hybrid -CE transistor Model, Determination of Hybrid -Conductances, CE Short Circuit Current gain, Parameters of  $f_{\beta}$  and fT, Frequency response of RC coupled CE amplifiers. n–Stage Cascaded Amplifier, Darlington pair, Cascode amplifier, CE-CC Amplifiers.

Transformer coupled amplifier, CE current gain with load

11 Hours Total: 48 Hours

### 12 Hours

#### 12 Hours

**13 Hours**

#### 3003

#### Textbook (s)

- 1. J.Millman, C.C.Halkias and Chetan D Parikh, Integrated Electronics, 2<sup>nd</sup> Edition, Tata McGraw Hill, 2017

- 2. Robert L. Boylestad and Louis Nashelsky, Electronic Devices and Circuits Theory, Pearson/Prentice Hall, 11<sup>th</sup> Edition, 2015

#### Reference (s)

- 1. A.Salivahanan, N.Suresh Kumar, A.Vallavaraj, Electronic Devices and Circuits, Tata McGraw-Hill Publish-ing Company Limited, 2<sup>nd</sup> Edition, 2008

- Visvesvara Rao, K. Bhaskara Rama Murty, K. Raja Rajeswari, P.Chalam Raju Pantulu, Electronic Devices and Circuits, Pearson Education, 2<sup>nd</sup> Edition, 2007

- 3. Millman and Grabel, Microelectronics, Tata McGraw Hill, 7thEdition, 2001

- 4. S.G.Burns and P.R.Bond, Principles of Electronic Circuits, Galgotia Publications, 2<sup>nd</sup> Edition, 1998

#### Sample Question (S)

#### **Internal Assessment Pattern**

| Cognitive Level | Int. Test 1 (%) | Int. Test 2 (%) | Open Book Exam (%) |

|-----------------|-----------------|-----------------|--------------------|

| Remember        | 20              | 20              |                    |

| Understand      | 55              | 40              |                    |

| Apply           | 25              | 40              | 60                 |

| Analyse         |                 |                 | 40                 |

| Evaluate        |                 |                 |                    |

| Create          |                 |                 |                    |

| Total (%)       | 100             | 100             | 100                |

#### Remember

- 1. List any two advantages of JFET over BJT.

- 2. Define Rectifiers. List any two types of Rectifiers.

- 3. Define stability factor, S.

- 4. Reproduce the symbol of n type JFET.

- 5. Reproduce the symbol of p type JFET.

- 6. Arrange emitter, base and collector in increasing order of doping concentration.

#### Understand

- 1. Explain the consequences due to applied reverse voltage at Collector junction in CB configuration.

- 2. Represent the structure of JFET and explain the operation of n channel JFET.

- 3. Illustrate the current components of BJT.

- 4. Interpret FET as a Voltage Controlled Device.

- 5. Compare compensation techniques for the variations in ICO due to temperature.

- 6. Explain about thermal runaway.

- 7. Explain the Breakdown Mechanism in Semiconductor Diodes.

- 8. Explain the working principle of Tunnel diode with its V-I characteristics.

#### Apply

- 1. Find the value of IC and IE of a transistor at room temperature for Ico=5 $\mu$ A, IB=100 $\mu$ A and  $\beta$ = 100, If the temperature is raised by 100°C.

- 2. A full wave rectifier is designed with a  $50\mu$ F capacitor in parallel with a  $500\Omega$  resistor. The transformer secondary voltage to centre-tap is 40V rms and 50Hz. The diode and transformer resistances may be ne-glected. Compute the followings:

- (i) Ripple factor of the rectifier-filter output

- (ii) % of load regulation

- (iii) Repeat (i) and (ii) if  $100\mu$ F capacitor in parallel with a 500 $\Omega$  resistor.

- 3. Design a Self-biasing circuit as shown in figure such that IC= 5mA, VCE=8V, VE=6V, S=10,  $\beta$ =200 and VCC=20V.

4. A circuit designer team-A has to design a biasing circuit using BC182 transistor. The purpose of biasing circuit is to produce faithful amplification to the input signal if the circuit operates in temperature range of 25°C to 75°C. The circuit designer team-B has provided the information to Team-B that if the operating point of the biasing circuit varies between (11.3mA, 5.67V) to (17mA, 2.48V) then also faithful amplifica-tion can be achieved. Design the biasing circuit.

5. A designer has to design a base resistor bias circuit for a CE amplifier such that operating point is VCE=8Vand IC = 2 mA. He is supplied with a fixed 15V d.c. supply and a transistor with  $\beta$  = 100. Take base-emitter voltage VBE = 0.6V and he has the liberty to use silicon or germanium transistor. Calculate also the value of load resistance that would be employed.

#### [Open Book Examination Question]

#### Analyse

1. Justify the small-signal voltage gain and input resistance of a common-emitter circuit with an emitter resistor.

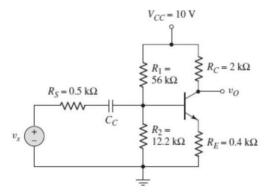

For the circuit in below figure, the transistor parameters are:  $\beta = 100$ , VBE(on) = 0.7 V.

2. A high frequency amplifier uses a transistor which is driven from a source with Rs=0. Calculate value of fH, if RL =0 and RL=1k $\Omega$ . Assume typical values of hybrid- $\pi$  parameters.

3. A circuit shown is to be a part of larger circuit which is expected to be operated at 25°C and 1000 Hz frequency. As a design engineer you are supposed determine the following parameters using the exact hybrid equivalent model and to prepare a detailed comparative analysis report of the results obtained using the approximate analysis.

- (a) Input impedance and overall input impedance.

- (b) Current gain and overall current gain.

- (c) Voltage gain and overall voltage gain.

- (d) Output impedance and overall output impedance.

[Open Book Examination Question]

#### 21EC302 Linear Circuit Analysis

#### **Course Outcomes**

- 1. Interpret the characteristics of RL, RC, RLC series and parallel circuits in both time and frequency domain

- 2. Compute the power and power factor of RL, RC, RLC series and parallel circuits

- 3. Design resonant circuits for a given frequency

- 4. Demonstrate the theorems to simplify complex networks

- 5. Assess the transient behaviour of RLC circuits

- 6. Compute the parameters of two port networks

#### **COs – POs Mapping**

| COs | PO <sub>1</sub> | PO <sub>2</sub> | PO <sub>4</sub> | PO <sub>5</sub> | PSO <sub>1</sub> |

|-----|-----------------|-----------------|-----------------|-----------------|------------------|

| 1   | 2               |                 | 1               | 2               | 2                |

| 2   | 3               | 2               | 1               | 2               | 3                |

| 3   | 3               | 2               | 2               | 2               | 3                |

| 4   | 3               | 2               | 2               | 2               | 3                |

| 5   | 3               | 2               | 2               | 2               | 3                |

| 6   | 3               | 2               | 2               | 2               | 3                |

3-Strongly linked | 2-Moderately linked | 1-Weakly linked

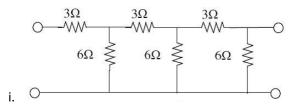

#### Unit I

#### **Sinusoidal Steady State Analysis**

Concept of Phasor and I notation, Impedance and Admittance – Time domain and frequency domain response of R, L, C series, parallel and series- parallel circuits to sinusoidal excitation. Computation of active, reactive, complex power and power factor, Series and parallel resonance of RLC circuits –Selectivity, bandwidth and quality factor-implications with voltage and current excitation. Incandecent Lamp, Tube light

#### **Practical Components**

- 1. Verification of series RLC circuits.

- 2. Verification of parallel RLC circuits.

- 3. Verification of Source power factor for the random RLC Circuit.

- 4. Verification of series Resonance circuits.

- 5. Verification of Parallel Resonance circuits.

#### Unit II

#### Network Theorems

Source transformation, Superposition, Thevinin's, Norton's, Maximum power transfer, Reciprocity, Tellegen's, Millman's and Compensation theorems for DC and AC excitations. Substitution theorem Miller's Theorem

#### **Practical Components**

- Analysis of linear circuits using superposition Theorem. 1.

- 2. Analysis of linear circuits using Thevenins Theorem.

- Analysis of linear circuits using Nortons theorem. 3.

- Alysis of linear circuits using Compensation Theorem. 4.

- Verification of Maximum power transfer theorem 5.

#### Unit III

#### **Transient Analysis**

D.C Transients: Transient response of R-L, R-C, R-L-C circuits for d.c excitation – initial conditions –solution using differential equations and Laplace transform approaches.

A.C Transients: Transient response of R-L, R-C, R-L-C circuits for sinusoidal excitation – initial conditions – Solution using Laplace transform approaches.

Transient behavior of RLC circuits for Impulse excitation, Transient behavior of RLC circuits for Ramp excitation

#### 13+10 Hours

#### 11+10 Hours

3024

#### **Practical Components**

- 1. Time constant of a RL (series & parallel) circuits.

- 2. Time constant of a RC (series & parallel) circuits.

#### Unit IV

#### **Network Parameters**

Two port networks, Impedance parameters, Admittance parameters, Transmission parameters, hybrid parameters – Interrelationship between parameters – Concept of transformed network – two port network parameters using transformed variables – Interconnection of two port networks. *BJT equivalent circuit, Characteristic impedance of Two port networks*

b) i equivalent circuit, churacteristic impedance of i wo port ne

#### **Practical Components**

- 1. Measurement of Impedance parameters of linear circuits.

- 2. Measurement of Admittance parameters of linear circuits.

- 3. Measurement of Hybrid parameters of linear circuits

- 4. Measurement of ABCD parameters of linear circuits

#### 9+8 Hours Total: 48+32 Hours

#### Textbook (s)

- 1. M.E Van Valkenburg, Network Analysis, Prentice Hall of India, 3<sup>rd</sup> Edition, 2015

- 2. W.H.Hayt, J.E.Kimmerly, and S.M.Durb, Engineering circuit analysis, McGraw Hill Education private limited, 8th Edition, 2013

#### Reference (s)

- 1. Gopal G. Bhise, Prem R. Chadha, Durgesh C. Kulshreshtha, Engineering Network Analysis and Filter Desgin, Umesh Publications, 2009

- Charles K Alexander, Mathew N.O Sadiku, Fundamentals of Electric circuits, Tata McGraw Hill, 5<sup>th</sup> Edition

- 3. Sudhakar A, Shyammohan S Palli, Circuits and Networks: Analysis and Synthesis, McGraw Hill, 5<sup>th</sup> Edition

#### Sample Question (S)

#### **Internal Assessment Pattern**